Menyimpan Bit Dengan Latch

02 November 2011 Tinggalkan komentar

Sirkuit yang outputnya tergantung pada input sebelumnya disebut sebagai sequential circuit. Ketergantungan dengan input sebelumnya membuat sequential circuit memiliki sifat memori. Salah satu contoh sequential circuit yang ditunjukkan dalam tulisan ini adalah apa yang disebut sebagai latches. Berikut ini adalah diagram sirkuit SR latch:

SR latch adalah sirkuit sederhana yang terdiri atas dua buah NOR gate. Sirkuit ini membutuhkan dua input, yaitu S (Set) dan R (Reset). SR latchmenghasilkan dua output, yaitu Q dan Q’.

Bila nilai S adalah 0 dan R adalah 1, maka nilai Q adalah 0. Hal ini karena R adalah 1 dan NOR gate akan selalu menghasilkan 0 bila salah satu input bernilai 1. Sebaliknya, nilai Q’ adalah 1.

Bila nilai S adalah 1 dan R adalah 0, maka keluaran Q’ selalu 0 sehingga Q bernilai 1.

Bila S bernilai 0 dan R bernilai 0, maka output dari Q dan Q’ akan bergantung pada nilai saat ini:

- Nilai Q adalah 1 dan Q’ adalah 0. Lalu, SR latch mendapat input S berupa 0 dan R berupa 0, maka nilai Q menjadi 1 dan nilai Q’ menjadi 0.

- Nilai Q adalah 0 dan Q’ adalah 1. Lalu, SR latch mendapat input S berupa 0 dan R berupa 0, maka nilai Q menjadi 0 dan nilai Q’ menjadi 1.

Hal ini menunjukkan bahwa:

- Bila Set (S) bernilai 1 dan Reset (R) bernilai 0, maka nilai Q akan menjadi 0.

- Bila Set (S) bernilai 0 dan Reset (R) bernilai 1, maka nilai Q akan menjadi 1.

- Bila Set (S) bernilai 0 dan Reset (R) bernilai 0, maka nilai Q akan selalu sama seperti nilai sebelumnya.

Dengan demikian, sebuah SR latch dapat dipakai untuk menyimpan nilai sebuah bit. Untuk mengatur nilai bit, seseorang perlu memberikan SR = 10 atau SR = 01. Untuk mempertahankan nilai bit tersebut, nilai S tetap 0 dan nilai R tetap 0, maka bit Q akan selalu memiliki nilai yang sama selama listrik masih mengalir. Ini adalah konsep dasar dari sebuah sel 1-bit dalam memori RAM.

Sequential circuit umumnya beroperasi pada synchronous mode. Pada modus ini, seluruh sirkuit dalam sistem mengubah state-nya secara bersamaan pada waktu yang telah ditentukan, melalui penggunaan clock signal. Sebuah clock signal adalah sinyal yang memiliki state 1 (ON) dan 0 (OFF), seperti yang ditunjukkan pada gambar berikut:

Sebuah clock cycle adalah waktu diantara dua buah rising edge (sisi sinyal dari 0 menjadi 1) yang berurutan. Clock rate atau frequency adalah jumlah clock cycle selama 1 detik dalam satuan Hertz (Hz). Dengan demikian, frequency 1 GHz menunjukkan bahwa dalam 1 detik terdapat 1 x 109 clock cycle. Jadi, waktu yang dibutuhkan untuk sebuah clock cycle adalah 1 / (1 x 109) = 1 x 10-9 detik atau 1 ns (nano detik).

Untuk membuat SR latch tersinkronisasi dengan keseluruhan sirkuit lainnya dalam sistem, maka diagram dapat dimodifikasi menjadi seperti pada gambar berikut:

Sekarang, input pada SR latch akan memiliki efek bila terdapat sinyal 1 (ON) dari clock.

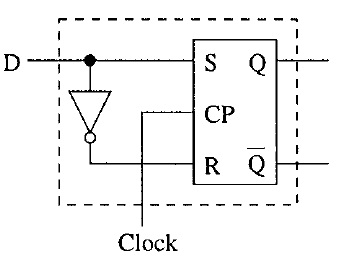

D latch adalah jenis SR latch yang menghindari kombinasi S=1 dan R=1. Caranya adalah dengan menggunakan sebuah inverter, seperti yang terlihat di gambar berikut:

Langkah untuk memberi nilai Q pada D latch sama seperti pada SR latch. Setelah itu, nilai Q pada D latch akan terus dipertahankan dengan selama sinyal dari clock adalah sinyal 0 (OFF).

Anda harus log masuk untuk menerbitkan komentar.